Research Overview

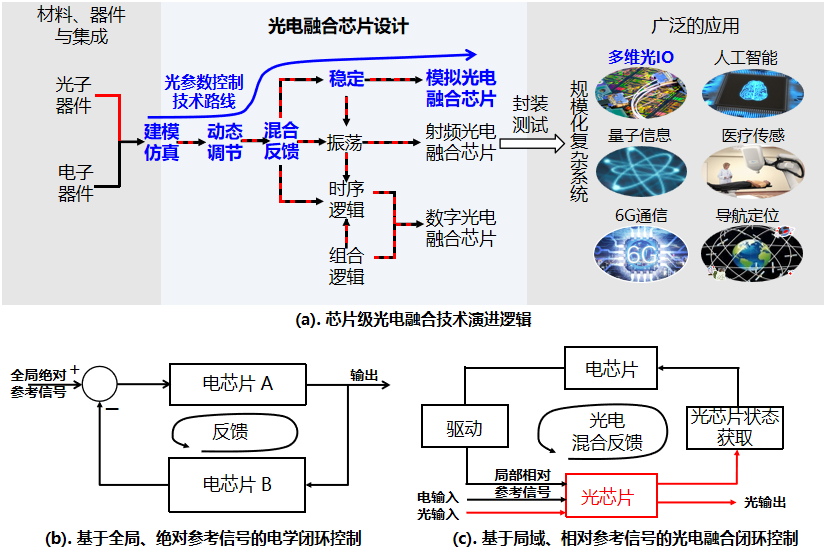

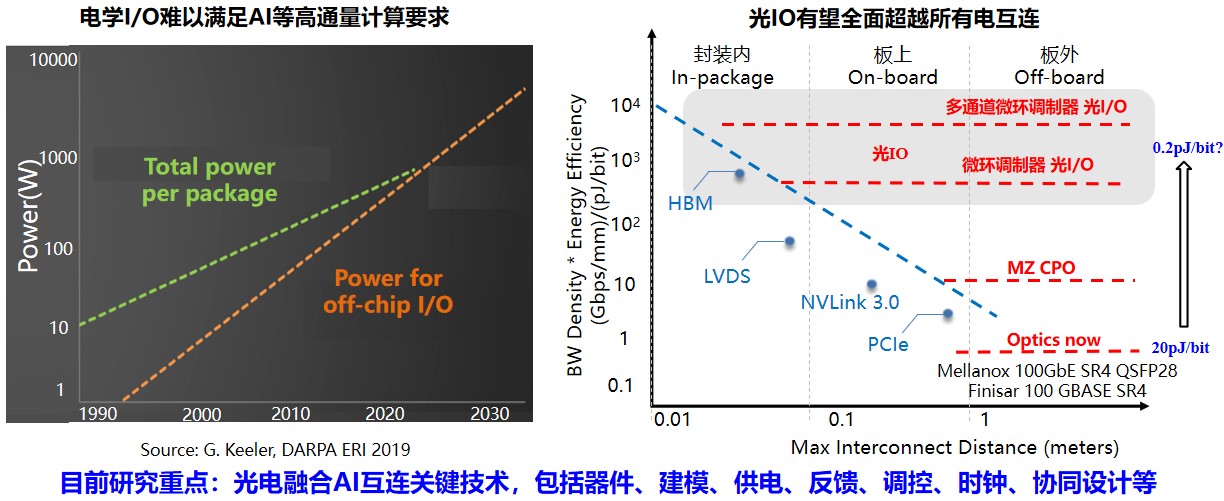

We are interested in Fast, Reliable, Energy-Efficient (FREE), and Scalable integrated circuits for manipulation of and interaction between electrons and photons with applications to communication, computing, and sensing. We have proposed the Electronic-Photonic Heterogeneously-converging IC (EPHIC) framework that combines integrated photonics and integrated electronics at the circuit level by leveraging the experiences of electronic integrated circuits. In particular, we are interested in the following fundamental research directions:

- Power, energy, and thermal problems in silicon photonics.

- On-chip hybrid closed-loop photonic parameter stabilization.

- Fundamental design theory and basic IC building blocks.

- AI for EPHIC design automation and EPHIC for AI systems.

- Electronic-phototonic heterogeneously-converging chiplet.

- Ultra-low-loss waveguides and high efficiency optical coupling.

- Miniaturized equipments for photonic parameter measurement.

- Uncertainty characterization and quantification of photonic devices.

Current Research Topics

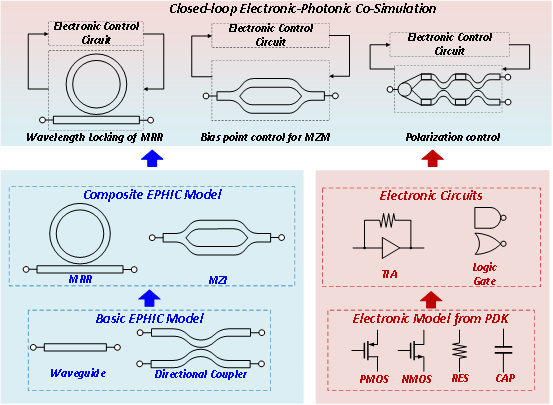

Photonic Device Modeling and Electronic-Photonic Co-Simulation

Electronic-photonic co-simulation is an important condition for the future large-scale commercialization of electronic-photonic heterogeneous-converging ICs (EPHICs), which can greatly improve design efficiency. Photonic device models can be implemented using various methods, such as scattering parameters and analytic models, on platforms like EDA, PDA, and MATLAB. Verilog-A and SPICE are popular languages for photonic modeling in the EDA platform. The Verilog-A photonic models [1-3] are used for photonic devices like microrings, Mach-Zehnder interferometers, and nonlinear effects, but require extra time for compiling when co-simulating with SPICE-based electrical models. The SPICE-compatible photonic models [4] can improve efficiency and have the potential to support large-scale closed-loop electronic-photonic co-simulations.

References

[1] Da Ming, Zhicheng Wang, Lining Zhang, M. Tan*, “A Verilog-A compact model for silicon micro-ring supporting fast thermal-electronic-photonic co-simulation,” in the 10th Int. Conf. on Information Optics and Photonics (CIOP), Beijing, China, Jul., 2018.

[2] Yuhang Wang, Da Ming, M. Tan*, “Closed-loop thermal-electronic-photonic co-simulation for a novel Mach-Zehnder modulator bias control scheme”, in the 11th Int. Conf. on Information Optics and Photonics (CIOP), Xi'an, China, Jul., 2019.

[3] Siyuan Zhang, Xiaolong Fan, Nuo Chen, Ciyuan Qiu, Xingsheng Wang, Ken Xingze Wang, Jing Xu, and M. Tan*, “ Compact photonic model based on coupled-mode theory for nonlinear interactions in electronic-photonic co-simulation,” Opt. Express (OE), vol. 32, no. 16, pp. 27599-27613, 2024.

[4] Da Ming, Yuhang Wang, Zhicheng Wang, Ken Xingze Wang, Ciyuan Qiu, and M. Tan*, “EPHIC models: general SPICE photonic models for closed-loop electronic-photonic co-simulation,” IEEE Trans. Circuits Syst. I Regul. Pap., (TCAS-I), vol. 71, no. 4, pp. 1819 - 1831, 2024

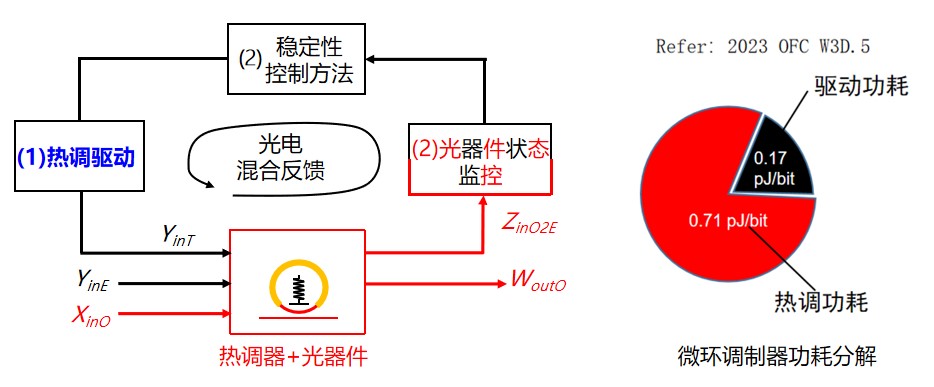

Power and Thermal Management of EPHIC

All active integrated photonic devices, (e.g. laser diode, photodiode, etc.), need power supply. Furthermore, almost all resonator photonic devices need thermal control to maintain a fixed resonant frequency. Also, thermal tuning is one of the most commonly used methods to control on-chip photonic parameters. At last, the related electronic building blocks require power supplies. Power and thermal control is an indispensable part of EPHIC.

References

[1] Z. Xie, K. Ye, K. X. Wang, Q. Cheng, and M. Tan*, “A time-division-multiplexed clocked-analog low-dropout regulator,” IEEE Trans. Circuits Syst. I Regul. Pap., (TCAS-I), vol. 68, no. 3, pp. 1366–1376, Jan. 2021.

[2] Siyuan Zhang, K. X. Wang, and M. Tan*, “An eight-channel switching-linear hybrid dynamic regulator with dual-supply LDOs for thermo-optic tuning,” IEEE Trans. Circuits Syst. I Regul. Pap., (TCAS-I), vol. 69, no. 8, pp. 3428 - 3437, May 2022.

[3] Tianchi Ye, Kaixuan Ye, Ziying Xie and M. Tan*, “A four-channel TDM clocked-analog LDO using a shared compensation block for thermo-optic tuning,” IEEE Trans. Circuits Syst. I Regul. Pap., (TCAS-I), vol. 71, no. 3, pp. 1050-1060, May 2024.

[4] M. Tan* et al., “Towards electronic-photonic-converged thermo-optic feedback tuning,” J. Semicond., vol. 42, no. 2, p. 23104, 2021.

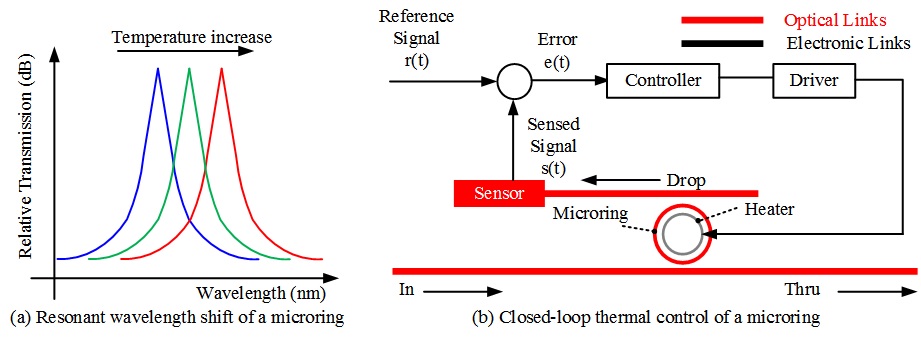

On-Chip Stabilization of Photonic Parameters

Photonic parameters (e.g. wavelength, phase, etc.) are sensitive to fabrication variations, temperature, cross talk, and so on. Due to both random and systematic variations, it is difficult to resolve this challenge by improving the fabrication process alone [2]. On-chip stabilization of photonic parameters is the key to practice and large-scale integrated photonic systems. On-chip closed-loop electronic-photonic feedback control so far seems to be the only way to resolve this above challenge effectively.

References

[1] M. Tan*, Y. Wang, K. X. Wang*, Y. Yu, and X. Zhang, “Circuit-level convergence of electronics and photonics: basic concepts and recent advances,” Front. Optoelectron., vol. 15, no. 1, pp. 1-17, 2022.

[2] Zhicheng Wang, Da Ming, Yuhang Wang, Ciyuan Qiu, and M. Tan*, “ Resolving the scalability challenge of wavelength locking for multiple micro-rings via pipelined time-division-multiplexing control,” Opt. Express (OE), vol. 30, no. 14, pp. 24984-24994, 2022.

[3] Zhicheng Wang, Da Ming, Yuhang Wang, Ken X. Wang, Xi Xiao, Xinliang Zhang and M. Tan*, “ An electronic-photonic converged adaptive-tuning-step pipelined time-division-multiplexing control scheme for fast and scalable wavelength locking of micro-rings,” J. Light. Technol. (JLT), vol. 40, no. 16, pp. 5622 - 5630, 2022.

[5] Yuhang Wang, Da Ming, M. Tan*, “Closed-loop thermal-electronic-photonic co-simulation for a novel Mach-Zehnder modulator bias control scheme ”, in The 11th Int. Conf. on Information Optics and Photonics (CIOP), Xi'an, China, Aug., 2019

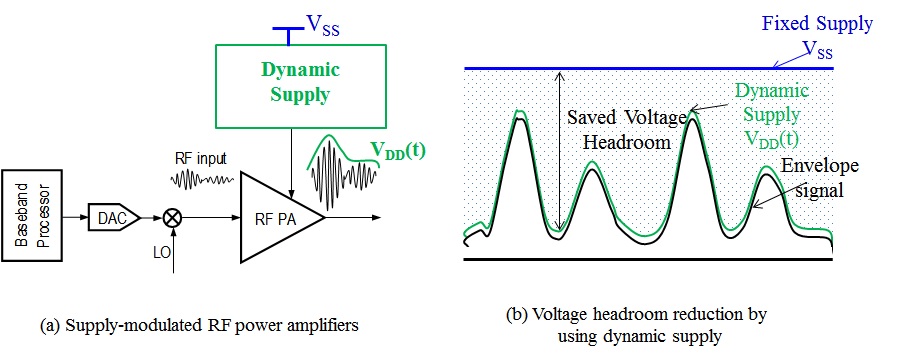

Dynamic Power Supply for 5G/IoT

The orthogonal frequency division multiplexing (OFDM), which is the key technology for

5G/NB-IoT wireless

commutations, suffers from the high peak-to-average power (PAPR) ratio [1]. To maintain sufficient linearity

under a

high PAPR, the RF power amplifier (PA) has to use a large power back-off, which degrades the efficiency

significantly. This linearity and efficiency tradeoff problem is widely recognized as one of the key challenges

for 5G/NB-IoT wireless systems. Supply-modulated RF PA [2] is one of the most promising techniques to resolve this

challenge but critically relies on a wide bandwidth high-efficiency supply modulator. Both linear regulator and

switching regulator fail to meet these two requirements simultaneously. The hybrid

supply modulator (HSM), which combines a linear regulator and a switching regulator

in parallel, is a promising solution to achieve both high linearity and high

efficiency. We have proposed several novel HSM architectures [3],[4].

References

[1] T. Jiang and Y. Wu, “An overview: Peak-to-average power ratio reduction

techniques for OFDM signals,” IEEE Trans. Broadcast., vol. 54, no. 2,

pp. 257–268, Feb. 2008.

[2] B. Kim, J. Kim, D. Kim, J. Son, Y. Cho, and B. Park, “Push the envelope:

Design concepts for envelope-tracking power amplifiers,” IEEE Microw.

Mag., vol. 14, no. 3, pp. 68–81, Mar. 2013.

[3] M. Tan and W.-H. Ki, “An efficiency-enhanced hybrid supply modulator with single-capacitor

current-integration control,” IEEE J. Solid-State Circuits (JSSC), vol. 51, no. 2, pp. 533–542, Feb. 2016.

[4] M. Tan and W.-H. Ki, “ A 100MHz hybrid supply modulator with ripple-current-based PWM control ,” IEEE

J. Solid-State Circuits (JSSC), vol. 52, no. 2, pp. 569–578, Feb. 2017.

[5] Yifan Zhang, M. Tan*, “A buck converter using a fully-integrated current-mode dual-path type-III

compensator for NB-IoT applications”, in Proc. IEEE Int. Conf. on Integrated Circuits, Technologies and

Applications (ICTA), Beijing, China, Jul., 2018

Basic IC Building Blocks

We have proposed a number structures for two-stage [1],[2] and three-stage amplifiers

[3]. Furthermore, we have established a

generic model [4] that links the compensation techniques used in two-stage amplifiers to the structures of

three-stage

amplifiers. Our previous results provide a solid foundation for further investigation of amplifiers and other

basic

IC building blocks.

References

[1] M. Tan and W.-H. Ki, “Current-mirror Miller compensation: An improved frequency compensation

technique for two-stage amplifiers,” in International Symposium on VLSI Design, Automation, and Test (VLSI-DAT),

Hsinchu, Taiwan, pp. 312-315, Apr. 2013.

[2] M. Tan and W.-H. Ki, “Split-output miller-compensated two-stage amplifiers,” in IEEE International

Conference of Electron Devices and Solid-state Circuits (EDSSC), Hong Kong, China, Jun. 2013.

[3] M. Tan and W.-H. Ki, “A cascode Miller-compensated three-stage amplifier with local impedance

attenuation for optimized complex-pole control,” IEEE J. Solid-State Circuits (JSSC), vol. 50, no. 2, pp.

440–449, Feb. 2015.

[4] M. Tan and W.-H. Ki, “A generic model for constructing three-stage amplifiers,” in IEEE International

Symposium on Circuits and Systems (ISCAS), Montreal, Canada, May 2016.